一.電磁干擾EMI問題:

目前廠內(nèi)常用到的CPU的RADIATION發(fā)射普遍比較高.特別是用到較高BUS頻率的HC08系列,如廠內(nèi)使用的MR32及GP32。CPU輻射成了EMI的瓶頸。

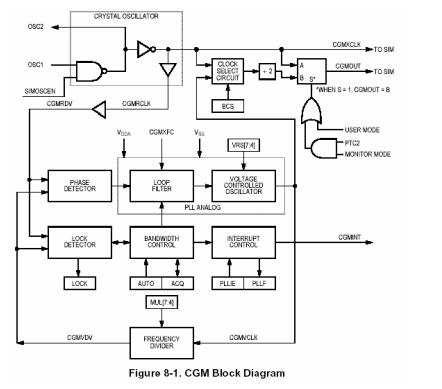

二.PLL部分

PLL鎖相環(huán)是將晶振倍頻升成BUS工作頻率的方塊,內(nèi)部方塊圖見右圖。由于為CPU內(nèi)高頻部分,它發(fā)射了大量的NOISE,我們可以探測到其發(fā)射的途徑有兩個:

(1)CPUPLL方塊的自身對外輻射。

(2)通過與PLL連接的TRACE形成的天線對外發(fā)射。

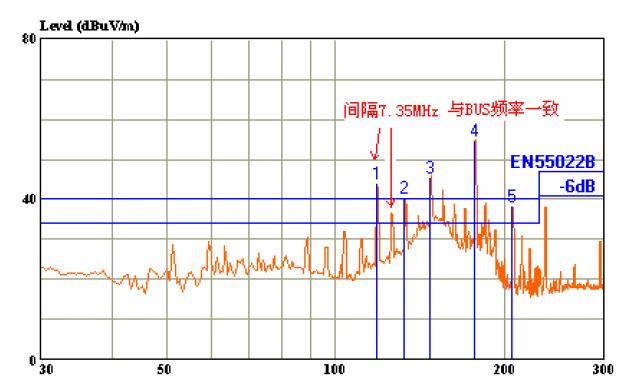

此部分的NOISE的特征為尖峰間隔等于內(nèi)部BUS頻率

7.35MHZ見下圖。

INVERTER CNTL中MR32的

RADIATION干擾

改善對策:

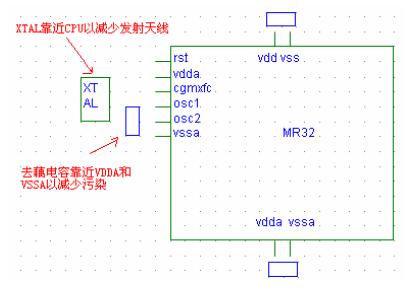

1.加強PLL外接的TRACE的去藕,將CGM方塊單獨的電源VDDA和VSSA的去藕貼片電容104移近CPU PIN腳以減少對TRACE的干擾,

2.晶振移近CPU以減少發(fā)射天線.

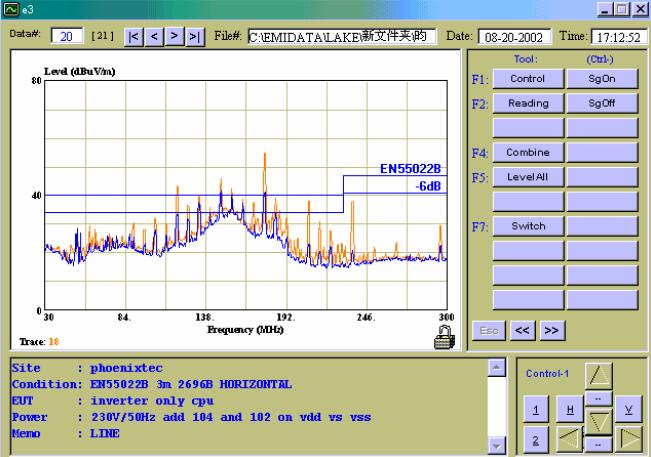

改善前后效果對比

讀數(shù)對比

三.長發(fā)射天線發(fā)射能力的抑制

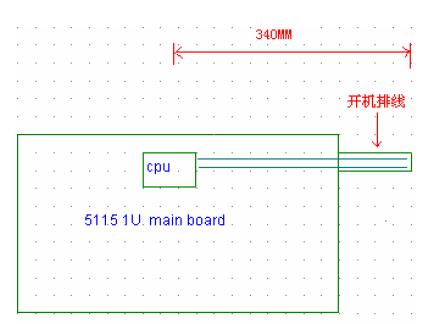

在應(yīng)用中,我們盡量減短與CPU相連的TRACE(發(fā)射天線)的長度,使其小于入/4,實際在51151U中,開機排線較長,其遠端離CPU為340MM.并且拔掉排線后輻射圖上有一頻段有明顯下降.

219MHz為干擾頻段中心:

入/4=0.25*1/219MHz=342MM與原端距離相符。

排線天線發(fā)射抑制前的RADIATION

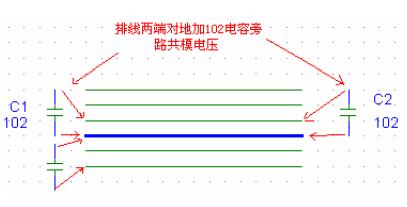

排線發(fā)射改善:

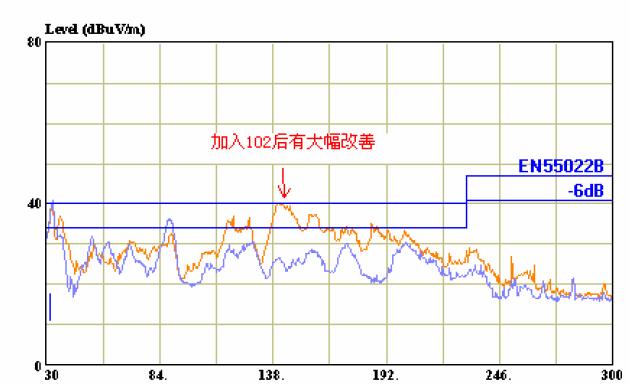

在開機10P排線的兩端各PIN對GND加102貼片電容,旁路排線上的共模電壓。

加電容抑制長天線發(fā)射后效果

四:高頻傳輸線反射及過激的抑制

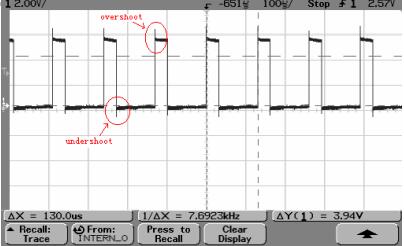

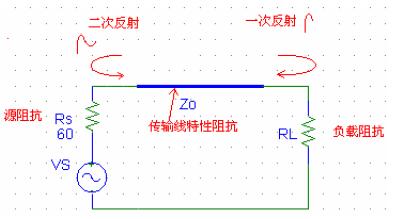

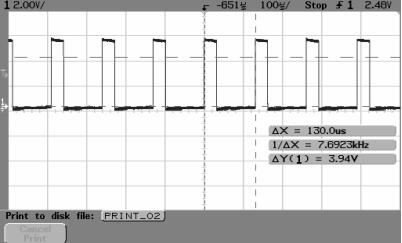

GP32在51151U應(yīng)用中,有一PIN腳作為SIN.pwm輸出,其頻率為7.6KHZ,我們發(fā)現(xiàn)其傳輸信號上有由于阻抗匹配問題導(dǎo)致過激震蕩現(xiàn)象,此過激震蕩引發(fā)EMI發(fā)射。

目前使用的CPU為CMOS工藝,上拉和下拉電阻都為600HM左右,但仍小于PCB TRACE的Zo(幾百OHM左右),在負載阻抗大時仍會產(chǎn)生反射震蕩。

有過激現(xiàn)象時的RADIATION

反射改善

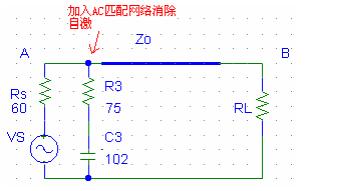

通過AC阻抗匹配(適用于周期出現(xiàn)的信號),在靠近CPU PIN腳加入RC網(wǎng)絡(luò)(R=Zo,C=102),可以很好地消除過激,如下圖。

實際測試中,發(fā)現(xiàn)去掉R也有相似的效果,故終采用102消除過激。

改善后EMI圖形

電磁干擾EMI設(shè)計結(jié)論:

1.通過對電源的正確去藕處理,及晶振部分的合理布線,可得到事半功倍的效果。

2.盡量減少長走線,避免形成強發(fā)射天線。

3.周期高頻信號線注意阻抗匹配,盡量避免走貫孔,形成阻抗斷點從而造成反射。

環(huán)測威專業(yè)解決產(chǎn)品電磁干擾EMI、電磁兼容EMC測試問題,提供設(shè)計指導(dǎo)和整改方案,詳情咨詢免費電話:4008-707-283

閱讀本文的人還閱讀了: